- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Strati epitassiali: la base dei dispositivi semiconduttori avanzati

Figura 1: illustra la correlazione tra concentrazioni di drogaggio, spessore dello strato e tensione di rottura per dispositivi unipolari.

La preparazione degli strati epitassiali di SiC comprende principalmente tecniche come la crescita per evaporazione, l'epitassia in fase liquida (LPE), l'epitassia a fascio molecolare (MBE) e la deposizione chimica in fase vapore (CVD), dove la CVD è il metodo predominante per la produzione di massa nelle fabbriche.

Tabella 1: Fornisce una panoramica comparativa dei principali metodi di preparazione dello strato epitassiale.

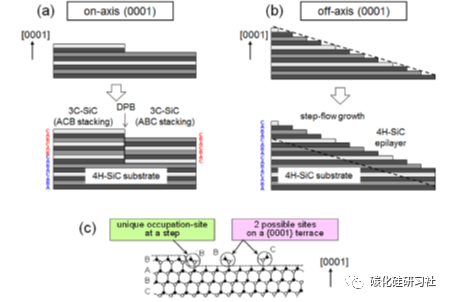

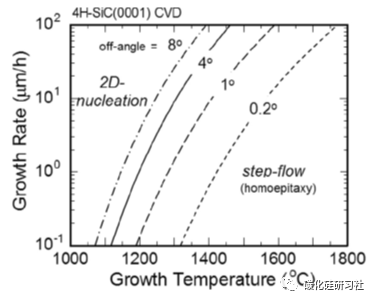

Un approccio innovativo prevede la crescita su substrati fuori asse {0001} con un angolo di inclinazione specifico, come illustrato nella Figura 2(b). Questo metodo aumenta significativamente la densità dei gradini riducendo al contempo le dimensioni dei gradini, facilitando la nucleazione principalmente nei siti di raggruppamento dei gradini e consentendo quindi allo strato epitassiale di replicare perfettamente la sequenza di impilamento del substrato, eliminando la coesistenza di politipi.

Figura 2: Dimostra il processo fisico dell'epitassia a gradini controllati in 4H-SiC.

Figura 3: Mostra le condizioni critiche per la crescita CVD nell'epitassia a gradini controllati per 4H-SiC.

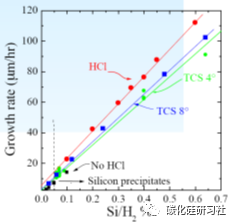

Figura 4: Confronta i tassi di crescita con diverse fonti di silicio per l'epitassia 4H-SiC.

Nel campo delle applicazioni a bassa e media tensione (ad esempio dispositivi a 1200 V), la tecnologia epitassiale SiC ha raggiunto uno stadio maturo, offrendo uniformità relativamente superiore in termini di spessore, concentrazione di drogaggio e distribuzione dei difetti, soddisfacendo adeguatamente i requisiti per SBD a bassa e media tensione , MOS, dispositivi JBS e altri.

Tuttavia, il settore dell’alta tensione presenta ancora sfide significative. Ad esempio, i dispositivi con tensione nominale di 10.000 V richiedono strati epitassiali di circa 100 μm di spessore, ma questi strati mostrano uno spessore e un'uniformità di drogaggio considerevolmente inferiori rispetto alle loro controparti a bassa tensione, per non parlare dell'impatto dannoso dei difetti triangolari sulle prestazioni complessive del dispositivo. Anche le applicazioni ad alta tensione, che tendono a favorire i dispositivi bipolari, impongono requisiti rigorosi sulla durata dei portatori minoritari, rendendo necessaria l'ottimizzazione del processo per migliorare questo parametro.

Attualmente, il mercato è dominato dai wafer epitassiali SiC da 4 e 6 pollici, con un graduale aumento della percentuale di wafer epitassiali SiC di grande diametro. La dimensione dei wafer epitassiali SiC è fondamentalmente determinata dalle dimensioni dei substrati SiC. Con i substrati SiC da 6 pollici ora disponibili in commercio, la transizione dall'epitassia SiC da 4 pollici a quella da 6 pollici è costantemente in corso.

Con l’avanzamento della tecnologia di fabbricazione dei substrati SiC e l’espansione delle capacità produttive, il costo dei substrati SiC sta progressivamente diminuendo. Dato che i substrati rappresentano oltre il 50% del costo dei wafer epitassiali, si prevede che la diminuzione dei prezzi dei substrati porterà a costi inferiori per l’epitassia SiC, promettendo così un futuro migliore per il settore.**